|

تضامنًا مع حق الشعب الفلسطيني |

بنية هارفارد

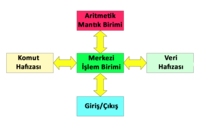

بنية هارفارد هي بنية حاسوبية تتميز بأن ذاكرة التعليمات وذاكرة البيانات مستقلتين عن بعضهما فيزيائياً.[1] وتستخدم كل ذاكرة منهما مسارات منفصلة للعنونة ونقل البيانات.

نشأ المصطلح من الحاسوب هارفارد مارك I، الذي كان يستخدم شريطاً مثقبّاً (بعرض 24 بت) لتخزين التعليمات، وعدادات إلكتروميكانيكية لتخزين البيانات. كان تخزين البيانات في هذه الأجهزة القديمة ينحصر بوحدة المعالجة المركزية، ولم يكن الوصول إلى التعليمات وتحميلها بشكل بيانات ممكناً. كما أن المعالج لم يكن قادراً على الإقلاع وحده، بل يجب أن يعمل شخص على تحميل البرامج.

تعتمد معظم المعالجات اليوم على مسارات منفصلة لزيادة الأداء، لكنها في الواقع تعتمد على بنية هارفارد معدلة، حيث تدعم هذه المعالجات مهاماً إضافية مثل تحميل برنامج من قرص تخزيني على أنه بيانات ثم تنفيذه.

تفاصيل الذاكرة

في بنية هارفارد لا يشترط أن تكون لذاكرتي التعليمات والبيانات الخصائص نفسها، إذ يمكن أن تختلفا عن بعضهما ببنية العنوان، أو طريقة التصنيع، أو التوقيت، أو عرض الكلمة.

في بعض النظم، يمكن تخزين التعليمات في ذاكرة قراءة فقط، بينما تحتاج البيانات عموماً لذاكرة قراءة/كتابة. كما أنه في بعض النظم تكون سعة ذاكرة التعليمات أكبر بكثير من ذاكرة البيانات، ولذلك تكون عناوين التعليمات أعرض من عناوين البيانات.

الاختلاف عن بنية فون نيومان

في بنية فون نيومان الأصلية، إما أن يقرأ المعالج تعليمة ووإما أن يقرأ أو يكتب البيانات على الذاكرة، لكن لا يمكن أن يجري الحدثين معاً لأن التعليمات والبيانات تمران على نفس النواقل في النظام. أما في الحواسيب ذات بنية هارفارد فيمكن لوحدة المعالجة المركزية قراءة تعليمة وتنفيذ عملية وصول للبيانات في آن معاً، حتى في حال عدم وجود ذاكرة مخبئية. ولذلك يمكن أن تكون حواسيب هارفارد أسرع بالنسبة للدارات المعقدة لأن عمليات جلب التعليمات والوصول للبيانات لا تتنافس على مسار نقل وحيد.

كما أن فضاء عنونة البيانات في بنية هارفارد منفصل عن فضاء عنونة التعليمات، فقد يكون عنوان التعليمة مُمثَّلاً بقيمة عرضها 24 بت، بينما تُمثَّل عناوين البيانات بقيم مؤلفة من 8 بت غير مرتبطة بالقيمة التي تمثل عناوين التعليمات.

الاختلاف عن بنية هارفارد المعدلة

تتشابه بنية هارفارد المعدلة مع بنية هارفارد كثيراً، حيث تسمح لوحدة المعالجة المركزية بالوصول إلى الذاكرة عبر ناقلين منفصلين (أو أكثر)، لكنها لا تركز على الفصل التام بين التعليمات والبيانات. أكثر التعديلات انتشاراً هي فصل الذاكرة المخبئية المستخدمة للتعليمات عن الذاكرة المخبئية المستخدمة لتخزين البيانات. عندما يتعامل المعالج مع الذاكرة المخبئية، يعمل وفق بنية هارفارد تماماً. لكن عند الوصول للذاكرة الرئيسية، يعمل وفق بنية فون نيومان (حيث تنقل التعليمات البرمجية كما تنقل البيانات، وهذه التقنية مهمة). هذا التعديل منتشر في المعالجات المعاصرة مثل معمارية ARM ومعمارية إكس 86. تصنف أحياناً هذه المعالجات ضمن بنية هارفارد دون الالتفات إلى أنها في الواقع بنية معدلة عن بنية هارفارد الأصلية.

من التعديلات أيضاً السماح لوحدة المعالجة المركزية بقراءة كلمات من ذاكرة التعليمات (مثل ROM أو الذواكر الوميضية) ومعاملتها كبيانات للقراءة فقط. تستخدم هذه التقنية في بعض المتحكمات الدقيقة، ومنها متحكمات Atmel AVR. تسمح هذه التقنية بالوصول للبيانات الثابتة، مثل السلاسل المحرفية أو function tables مباشرة، دون الحاجة لنسخها أولاً إلى ذاكرة البيانات، وهذا يساعد على الاحتفاظ بذاكرة البيانات صغيرة السعة (والمستهلكة للطاقة) للمتغيرات التي تحتاج للقراءة والكتابة. تستخدم تعليمات آلة خاصة لقراءة البيانات من ذاكرة التعليمات.

تصميم الذاكرة المخبئية المنفصلة

تستفيد تصاميم المعالجات الحديثة عالية الأداء من خصائص بنية هارفارد وبنية فون نيومان ، خصوصاً بنية هارفارد المعدلة ذات «الذاكرة المخبئية المنفصلة» المنتشرة جداً. تقسم ذاكرة المعالج المخبئية في هذا التصميم إلى قسمين: ذاكرة مخبئية للتعليمات وذاكرة مخبئية للبيانات. تستخدم بنية هارفارد عندما يتعامل المعالج مع الذاكرة المخبئية. أما إذا لم تكن البتات المطلوبة متوفرة في الذاكرة المخبئية، فسوف يتم إحضارها من الذاكرة الرئيسية، التي لا تقسم إلى أقسام منفصلة للتعليمات والبيانات، رغم أن النظام قد يحوي متحكمات منفصلة يمكن استخدامها للوصول المتوازي لذواكر RAM و ROM وذواكر (NOR) الوميضية.

بالتالي يستفيد النظام من ميزات بنية هارفارد عند التعامل مع الذاكرة المخبئية رغم أنه يستخدم بنية فون نيومان في النواحي الأخرى، مثل تحميل البيانات والتعليمات عبر متحكم الذاكرة نفسه.

الاستخدامات الحالية لبنية هارفارد

إن استخدام المعالجات ذات نظام الذواكر المخبئية الحديث الذي يعتمد على بنية هارفارد المعدلة قد خفض من أهمية الميزة الأساسية لبنية هارفارد (وهي الوصول المتوازي لأكثر من ذاكرة في النظام في آن واحد). ينحصر استخدام البنى القريبة نسبياً من بنية هارفارد الأصلية في بعض التطبيقات التي يكون توفير الكلفة والطاقة فيها –عبر إزالة الذواكر المخبئية منها– أهم من العبئ البرمجي الناجم عن استخدام فضاءات عنونة منفصلة للتعليمات والبيانات.

- تستخدم معالجات الإشارة الرقمية (بالإنكليزية: Digital signal processors، واختصاراً DSP) عادة لتنفيذ خوارزميات قصيرة ومحسنة بشكل كثيف لمعالجة الصوتيات أو المرئيات. تتفادى هذه المعالجات استخدام الذواكر المخبئية لأنها قد تؤدي لاختلاف سلوك النظام عند إعادة التنفيذ بشكل متكرر. كما تكون الصعوبات النسخ من فضاءات عنونة متعددة ذات أهمية ثانوية مقارنة بسرعة التنفيذ. لذلك، تتضمن بعض معالجات الإشارة الرقمية عدة ذواكر للبيانات لها فضاءات عنونة مستقلة لتسهيل المعالجة وفق أسلوب SIMD أو VLIEW. على سبيل المثال، تقدم معالجات TMS320 C55x من تكساس إنسترومنتس عدة نواقل متوازية للبيانات (اثنين للكتابة وثلاثة للقراءة) وناقل واحد للتعليمات.

- تتميز المتحكمات الدقيقة بالسعة الصغيرة لذاكرة البرامج (الذاكرة الوميضية) وذاكرة البيانات (SRAM)، وعدم وجود ذاكرة مخبئية، وتستفيد من بنية هارفارد لتسريع المعالجة عن طريق الوصول التفرعي للتعليمات والبيانات. بما أن الذاكرتين منفصلتين فقد تختلفان عن بعضهما بعرض الكلمة، فتكون التعليمات بعرض 16 بت والبيانات بعرض 8 بت مثلاً. كما أن هذا يسمح أيضاً بجلب التعليمات أثناء تنفيذ مهام أخرى. من الأمثلة نذكر متحكمات AVR من Atmel ومتحكمات PIC من شركة Microchip Technology.

وحتى في هذه النظم، من الشائع إضافة تعليمات خاصة للوصول إلى ذاكرة البرامج كما لو أنها بيانات للقراءة فقط، فهي معالجات تعتمد بنية هارفارد معدلة.

مراجع

- ^

Wayne Wolf (2008). Computers as Components: Principles of Embedded Computing System Design (بالإنكليزية) (الثانية ed.). بورلينغتون، ماساتشوستس، الولايات المتحدة: Morgan Kaufmann Publishers. p. 56. ISBN:9780123743978. Archived from the original on 2018-04-14.

{{استشهاد بكتاب}}: صيانة الاستشهاد: لغة غير مدعومة (link)