|

تضامنًا مع حق الشعب الفلسطيني |

قلاب (إلكترونيات)

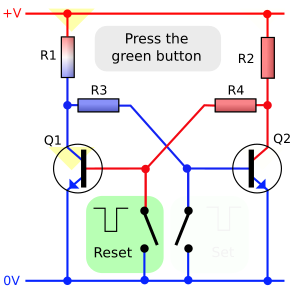

(R1, R2 = 1 kΩ; R3, R4 = 10 kΩ).

القلاب[1] أو القلابة[2][3] أو النطاطة[3] (بالإنجليزية: flip-flop) هو عنصر أساسي في دوائر المنطق التتابعي، يتأرجح القلاب بين حالتي استقرار حسب الدخل وحسب القيمة السابقة للخرج، بخلاف دوائر المنطق الترابطي التي يعتمد فيها الخرج على القيم الحالية للدخل فقط، [4] وبهذا يتصرف القلاب كذاكرة تحفط بت واحد من البيانات. تنقسم القلابات إلى نوعين، قلابات بسيطة، وقلابات ذات إشارة التزامن أو clocked flip-flops، (وتنقسم بدورها إلى متزامنة، غير متزامنة). رغم أن الاسم «قلاب» كان يشير لكلا النوعين إلا أنه يخصص حاليا للحديث عن الدوائر المتزامنة، في حين تعرف القلابات البسيطة باسم «المساكات».[5] [6]

مبدأ عمل القلاب

تبنى القلابات من البوابات المنطقية بأسلوب الارتجاع حيث ترجع القيم الخارجة من مجموعة من البوابات إلى دخل هذه الأخيرة مما يشكل حالة متزنة على آخر قيمة أعطيت لها

أنواع القلابات

- قلاب SR هو من أبسط أنواع القلابات، له دخل R يستعمل لتصفير القلاب (أي وضع القيمة 0 على الخرج Q للقلاب) وله دخل S لضبط القيمة 1 في خرج القلاب.

- قلاب السيد -التابع

- قلاب JK مثل القلاب ار اس لكن بوجود احتمالية الدخل J=1 وK=1 التي ينتج عنها عكس قيمة الخرج السابق

- قلاب T (قلاب مفصلي)

- قلاب D (قلاب التأخير)

استعمالاته

تستعمل القلابات أساسا في بناء الأنظمة الرقمية التي تعتمد على المنطق التتابعي مثل العدادات والسجلات وكذلك تستخدم في بناء الذاكرات المتطايرة RAM التي تعرف باسم كاش ميموري والعديد من التطبيقات المختلفة

قلاب SR

هناك صنف من الدارات المنطقية يعتمد خرجها في لحظة محددة على القيم السابقة لدخل الدارة بالإضافة إلى القيمة الحالية وهي لذلك تدعى بالدارات التتابعية إذ يتحدد سلوكها بتتابع قيم ودخلها حتى هذه اللحظة وبكلمات أخرى فإن لهذه الدارات ذاكرة تحتفظ فيها بماضيها الذي يتجسد في الحالة الداخلية للدارة. من ابسط الأمثلة على الدارات التتابعية باستخدام قلابات مختلفة أو ثنائيات الاستقرار (bi-stable). للقلاب حالتان داخليتان ممكنتان فقط (0 أو 1) وبالتالي يمكن تمثيل حالته الداخلية بمتحول ثنائي وحيد. ويكون للقلاب عادة خطا خرج يدعى أحدهما خط الصحة وقيمته هي قيمة الحالة الداخلية للقلاب والآخر هو متمم خط الصحة. من الواضح أنه يمكن تحقيق أية دارة تتابعية باستخدام الدارات التركيبية والقلابات.

القلاب من النمط rs:

و هو الأبسط ويدعى أحيانا قلاب ضبط – إعادة ضبط (Set-Reset) وله مدخلان فقط Sو R. فتطبيق دخل (بقيمة 1 منطقي) على المدخل S يؤدي إلى ضبط القلاب (يضعه في الحالة الداخلية 1) أما تطبيق دخل (بقيمة 1 منطقي) على المدخل R فيؤدي إلى إعادة ضبط القلاب على الحالة الداخلية 0 ويحتفظ القلاب بحالته السابقة عندما يطبق على مدخليه إشارة 0 منطقي وتكون حالته غير معروفة عندما يطبق على مدخليه إشارة 1 منطقي، لذلك يتم استبعاد هذه الحالة. يمكن الحصول على R-S-FLIP Flopباستخدام بوابتي NAND كمايلي

و الرمز المنطقي هو

و بشكل مشابه يمكن ان نشكل R-S Flip-Flopباستخدام بوابتي NAND فيكون كالتالي:

اما الجدول المنطقي هو:

و الرمز المنطقي له:

القلاب R-Sالمتزامن (Clocked R-S Flip-Flop (The :

يضاف إلى القلاب R-Sدخل يحمل إشارة الساعة للحصول على قلاب R-S المتزامن. الرمز المنطقي له:

و هو يكافئ اداة تستخدم بوابات NAND كما يوضح الشكل التالي

و لكن لابد من التأكيد على أن التطبيق التالي لـ RSFF يقاد بواسطة الأصفار. يمكن أن يرى بأن بوابتي NAND الإضافيتين تم وضعهما أمام القلاب SRFF القياسي. عندئذ لا تؤثر مداخل القلاب R وS على حالته إلا عندما تكون إشارة الساعة بقيمة 1 منطقي ويحتفظ القلاب بحالته الداخلية عندما تكون إشارة الساعة قيمة 0 منطقي.

القلاب السيد _التابع

يتكون القلاب السيد-التابع (THE MASTER-SLAVE FLIP –FLOP) من مغلاقين من النوع المبين (يسمى الأول منها بالسيد (MASTER) والثاني بالتابع (((SLAVE ومن بوابتي ادخال معطيات (1B) (1A) وبوابتي وصل (3A)و (3B) يتم عن طريقهما نقل المعطيات من المغلاق السيد إلى المغلاق التابع.

بما أن موجة الساعة المطبقة على بوابتي الدخل معاكسة للموجة المطبقة على بوابتي الوصل فإن هاتين المجموعتين سيعملان بشكل متناوب فعندما يتم تحرير بوابتي الدخل يتم إدخال المعطيات الموجودة على الطرفين (S)و (R) إلى المغلاق السيد. في هذه الأثناء تكون بوابتي الوصل مقيدتين لذلك لايحدث إي انتقال للمعطيات من المغلاق السيد إلى المغلاق التابع. في المرحلة التالية عندما تتحرر بوابتي الوصل وتقيد بوابتي الدخل يتم انتقال المعطيات إلى المغلاق التابع من المغلاق السيد بينما لاتدخل معطيات جديدة إلى المغلاق السيد. لضمان عدم عمل بوابتي الدخل وبوابتي الوصل في وقت واحد أثناء تغير مستوى الساعة من المنخفض إلى العالي وبالعكس يتم تحديد مستويات الجهود والتي تتحرر عندها هذه البوابات أو تقيد

في حال استخدام قلابات السيد التابع في الدارة نحصل على استجابة للدارة حيث تتم كتابة المعطيات الجديدة في المغلاق السيد للقلاب الأول دون حدوث تغيير في مستوى (Q1) وذلك عند أول تغيير في مستوى الساعة (الحافة 1) وعند الحافة الثانية (2) للساعة وبعد تأخير زمني قدره (TPD) تظهر المعطيات الجديدة على المخرج (Q1) كما تقيد بوابتي الدخل (1A) و (1B) للقلاب الثاني مباشرة. ولاتظهر أي استجابة من القلاب الثاني للتغيير في مستوى (Q1). بشكل مماثل يتم خلال الدور الثاني (الحاثة الثالثة والرابعة) نقل معطيات الدخل (S1=1 & R1=0) إلى القلاب الثاني. نظر الآن أي تغيير في مستوى خرج القلاب يحدث عند الحافة الهابطة لموجه الساعة جرة العادة على وضع خط فوق التسمية (clock) للإشارة إلى ذلك بينما تستخدم التسمية (clock) في الحالة التي تؤثر فيها الجبهة الصاعدة للموجة. تجهز القلابات السيد _التابع في كثير من الأحيان بمداخل التحكم بوضعية القلاب بصورة مستقلة عن إشارة الساعة وتسمى هذه المداخل الغير متواقته بالمداخل المباشرة (direct inputs).

يتم وصل الطرف (rd) بكل مغلاق إلى مدخل واحد يمكن بواسطته وضع القلاب في الوضعية (reset) كذلك يتم وصل الطرفين (sd) لتشكيل مدخل وضع القلاب في الوضعية (set). عندما يصبح (rd=0) و (sd=1)ينتقل القلاب إلى الوضعية reset وعندما يصبح (td=1) و (sd=0) ينتقل القلاب إلى الوضعية (set)بغض النظر عن مستويات المداخل (s)و (r)والساعة. وعندما تكون (sd=1)و (rd=1)فإن وضعية القلاب تصبح تابعة لمستويات (s)و (r)والساعة. أما الحالة (rd=0)و (sd=0)فيجب أن لا تستخدم.

ومع افتراض أن القلاب كان في الوضعية (RESET)عند ورود أول نبضة للساعة نلاحظ بأن التغير في مخرج القلاب يحدث دائما عند الجبهة الهابطة لنبضة الساعة. فعند نهاية النبضة الأول لدينا (S=1)و (R=0)لذا ينتقل القلاب إلى الوضعية (SET) ويحافظ على هذه الوضعية حتى نهاية النبضة الثانية بالرغم من أن مستوى (S)و (R)يتغير في هذه الفترة.

عند بداية النبضة الثانية حيث لدينا (S-0) و (R=1)ينتقل القلاب السيد إلى الوضعية RESET وعند الجبهة الهابطة لهذه النبضة يتم نقل وضعية (RESET)من المغلاق السيد إلى المغلاق التابع وهكذا عند الجبهة الهابطة للنبضة الثالثة يصبح المخرج (Q=1).وعند الجبهة الهابطة للنبضة الرابعة لايحدث تغي في مستوى (Q)لأن (S=R=0).وأخيرا عند نهاية النبضة الخامسة يصبح (Q=0)لأن (S=0)و (R=1).

القلاب J-K

تعتبر دارة القلاب JK من أكثر أنواع القلابات استخداماً. والرمزان المعتمدان J،K هما مجرد رمزين، وليسا اختصاراً لأية كلمة. ويمثلان الدخل. ويعتبر تطويرا للقلاب S-R حيث لا توجد به الحالة المستحيلة.[7]

يماثل القلاب S-R المتزامن في عمله من حيث الأوضاع الثلاثة الأولى للتشغيل، وهي:

- الحفاظ (عدم التغير).

- الحالة الفعالة (SET).

- الحالة غير الفعالة (RESET).

- أما الاختلاف فيأتي في الحالة الأخيرة حيث لا يوجد لديه حالة مستحيلة كما في القلاب (S-R).

دارة القلاب J-K

دارة القلاب J-K : مؤلفة من " 4 " بوابات بوابة اقتران سالبة، ويلحظ استخدام المؤقت أو نبضة الساعة CLK، للتزامن.

أما الرمز المنطقي لهذه الدارة فهو على الشكل المجاور.

ملاحظة: الاختلاف بين دارة القلاب J-K ودارة القلاب S-R أن الخرجين Q،Q موصولان إلى الدخل مرة أخرى.[8][9][10]

ويمكن كتابة المعادلة المميزة لهذا القلاب كالتالي:

جدول الحقيقة

| جدول الحقيقة للقلاب J-K | ||||

| J | K | Qالتالية | ملاحظات | |

| 0 | 0 | Q | حفاظ | |

| 0 | 1 | 0 | Reset | |

| 1 | 0 | 1 | Set | |

| 1 | 1 | Q | تبديل | |

يتضح من الجدول

- في السطر الأول أن حالة (0 0) يقابلها «حفاظ»

- في السطر الثاني: حالة (0 1) يقابلها قيمة (0) على الخرج Q ما يسمى " reset ".

- في السطر الثالث: حالة (1 0) يقابلها قيمة (1) على الخرج Q ما يسمى " set ".

- أما السطر الرابع فيبين حالة هامة من حالات القلاب J-K تسمى وضع «التبديل»

حيث ينعكس الخرج Q عن وضعه السابق عندما تصله نبض التزامن CLK. وهنا يتضح الفرق بين القلاب S-R والقلاب JK. حيث تم تجاوز الحالة المستحيلة «حالة الخطر» التي يصلها القلاب S-R مع قيم (1 1) للدخلين.

دور نبضة التزامن CLK

لا بد من ايضاح دور نبضة التزامن أو بالأحرى معنى التزامن ككل... نميز بين الدارات المنطقية التركيبية والدارات المنطقية التتابعية:

الدارات المنطقية التركيبية: (Combinational Logic Circuits) وفيها يعتمد خرج الدارة في أية لحظة على المدخلات المجودة في تلك اللحظة. الدارات المنطقية التتابعية:(Sequential Logic Circuits): ويتميز هذا النوع من الدارات بوجود ذاكرة حيث يعتمد خرج الدارة في لحظة ما على الدخل المطبق والخرج السابق لهذه الدارة. إن كلمة التزامن تعني أن الخرج سوف يتغير فقط عند نقطة محددة من نبضات التزامن أو نبضات الساعة CK أي التغير متزامن مع نبضات الساعة، والقلاب J-K المدروس يعمل مع الجبهة الهابطة، لنبضات الساعة. ولا يعمل إذا لم تصله هذه النبضة.

القلاب المفصلي

القلاب المفصلي (بالإنجليزية: Toggle flip-flop) المشهور تــ ((t flip-flop)) هو عبارة عن دارة إلكترونية منطقية لها مخرج يأخذ إحدى حالتين مستقرتين فقط إما (1) أو (0) حيث تتحدد قيمة المخرج وتبقى قيمة المخرج مخزنة حتى مع غياب إشارة الدخل وذلك بسبب وجود ماسك Latch للقيمة في البنية التصميمية للقلاب ويتم لتحكم بالمعلومات الداخلة والخارجة من القلابات بواسطة نبضات الساعة.

- والقلاب T هو عبارة عن القلاب JK إذا وصل مدخلاه بصورة دائمة على القيمة (1) (أي تكون J=K=T) حيث يعمل القلاب عندها على عكس الحالة السابقة للمخرج (Q). فعندما تكون (Q=1) فإن (Qn+1=0). والعكس صحيح ويكون ذلك مع كل نبضة ساعة.

أما التابع المنطقي له فهو على الشكل التالي بعد الاختصار بمخطط كارنوف: T*Q) +*Qn+1=TQ)

- حيث Q* هي نفي T.

- أي عندما يكون (j=k=0)..عندها يكون المخرج كما كان في الحالة السابقة

أما عندما يكون (J=K=1)) عندئذ يكون المخرج كما كان في الحالة السابقة.

- يملك القلاب T مدخلا آخرا موجود في كل القلابات السابقة وهو مدخل نبضات الساعة (Clock pulses) وهي النبضات الضرورية لنقل حالة المخارج من الوضعية الراهنة إلى الوضعية التالية ويستخدم القلاب Tفي تصميم الدارات التتابعية.

مثل: العدادات، مسجلات الإزاحة، مسجلات التخزين، المشفرات ومقسمات التردد ويستخدم في تصميم الذاكرات الالكترونية (ROM) وفاكات الشيفرة.

ان إشارة المدخل tc تسمح للنبضة بأن تطبق على المدخل T للقلاب مع كل نبضة تصل للقلاب من مولد النبضات يسبب تغيير حالة القلاب

قلاب التأخير

قلاب التأخير (بالإنجليزية: Delay flip-flop) أو D flip-flop دائرة إلكترونية من صنف الـقلابات (انظر قلاب)، تقوم بتأخير المعلومة الواردة إليه زمنياً، ونتحصل عليه بإيصال مدخلي الجي كاي فليب فلوب مع بعضهما البعض. و تتميز انك إذا وضعت على المدخل صفر منطقي يكون لعلى الخرج بعد أول نبضة ساعة صفر منطقي و إذا وضعت واحد منطفي يكون علي الخرج بعد أول نبضة ساعة واحد منطقي وبالتالي هي تعتبر واحد ذاكرة حيث يمكنها أن تحتفظ ب 1 بت وإذا جمعنا 8 دي فيب فلوب أصبح عندنا مسجل (ريجيستر) 1 بيت وهي بالفعل تستخدم ذاكرة في الحاسوب وكذاكرة كاش وو ذلك لسرعتها فمجرد وضع الإشارة (0 أو 1) يتم حفظها على الفور. ولكن يعيبعا أنها تعتبر كبير في الحجم لذا تستخدم في الكاش فقطو حيب أن الدي فليب فلوب عبارة عن 2 لاتش وكل لاتش مكونة من بوابتين نور أو بوابتين ناند وكل بوابة مكونة من أكثر من ترنزيستور أما في الذاكرة العشوائية فيتم استخدام المكثف لانه يحتاج مساحة أقل ولكنه في نفس الوقت يحتاج فترة أكبر لشحنه بالشحنة المناسبة.

انظر أيضا

المراجع

- ^ Q108408025، ص. 222، QID:Q108408025

- ^ Q115209924، ص. 59، QID:Q115209924

- ^ أ ب Q123703339، ص. 97، QID:Q123703339

- ^ Vai، M. Michael (2000). VLSI Design. CRC Press. ص. 147. ISBN:0849318769. مؤرشف من الأصل في 2017-03-24.

- ^ Latches and Flip Flops (EE 42/100 Lecture 24 from Berkeley) "...Sometimes the terms flip-flop and latch are used interchangeably..." نسخة محفوظة 05 أكتوبر 2016 على موقع واي باك مشين.

- ^ Pedroni، Volnei A. (2008). Digital electronics and design with VHDL. Morgan Kaufmann. ص. 329. ISBN:978-0-12-374270-4. مؤرشف من الأصل في 2020-02-29.

- ^ Hinrichsen، Diederich؛ Pritchard، Anthony J. (2006). Mathematical Systems Theory I: Modelling, State Space Analysis, Stability and Robustness. Springer. ص. 63–64. ISBN:9783540264101. مؤرشف من الأصل في 2014-06-29.

- ^ Wu، Haomin؛ Zhuang Nan (1991). "Research into ternary edge-triggered JKL flip-flop". Journal of Electronics (China). ج. 8 ع. Volume 8, Number 3 / July, 1991: 268–275. DOI:10.1007/BF02778378.

- ^ Bowdon، Edward K. (1960). The design and application of a "flip-flap-flop" using tunnel diodes (Master's thesis). University of North Dakota. مؤرشف من الأصل في 2020-02-29.

- ^ Improvements in ionic relays" British patent number: GB 148582 (filed: 21 June 1918; published: 5 August 1920). نسخة محفوظة 12 أكتوبر 2008 على موقع واي باك مشين.

| في كومنز صور وملفات عن: قلاب |